Wishbone Systembus

Author: Claus Janicher 2025

This is a wishbone template module, which allows a simple copy paste or module extension for your slave systembus participant. The template has three dummy registers and you can use an address offset to access them. The byte select functionality is also implemented.

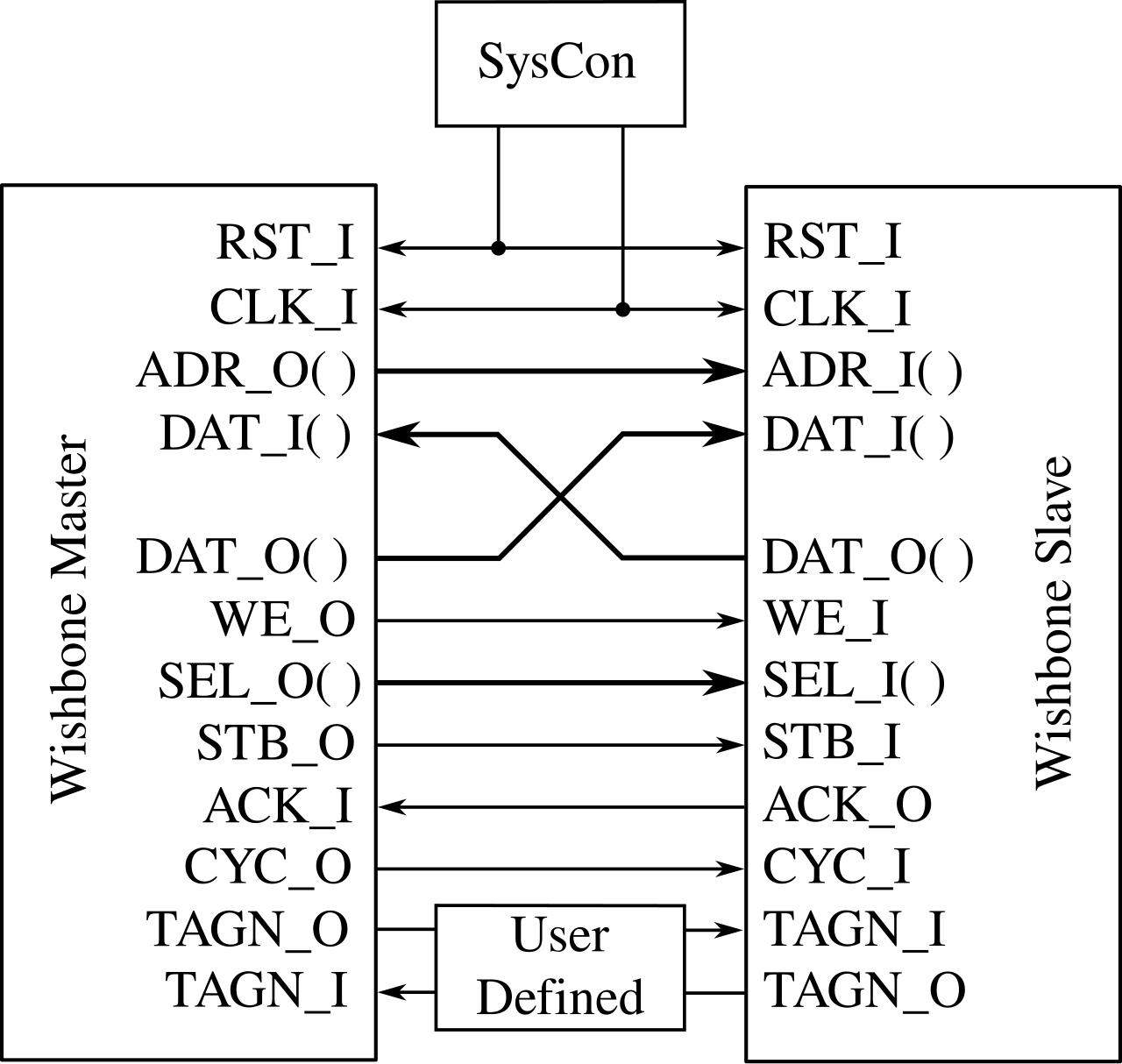

Overview

The general wishbone bus signal overview is displayed in the image below.

Fig. 10 Diagramm of the Wishbone bus interface.

-

SC_MODULE(m_wishbone_t)

This module is the hardware-wishbone SLAVE unit which can be used for the hardware implementation of any systembus peripherals. It is the interface between the wishbone master (currently HW_MEMU) and your custom peripheral module.

This Implementation shows the wishbone slave usage with three subaddresses. This means the master can directly access your slave subregisters, that are defined in the e_wb_addressrange enumeration type.

- Ports:

- Parameters:

clk – [in] clock of the module

reset – [in] reset of the module

wb_adr_i – [in] Wishbone Adress input

wb_dat_o – [out] Wishbone Data out

wb_dat_i – [in] Wishbone Data in

wb_we_i – [in] Wishbone Write-Enable in

wb_stb_i – [in] Wishbone Strobe in

wb_cyc_i – [in] Wishbone Cycle in

wb_ack_o – [out] Wishbone ACK input

wb_cti_i – [in] // Wishbone cycle type identifier (optional, for registered feedback)

wb_bte_i – [in] // Wishbone burst type extension (optional, for registered feedback)

wb_err_o – [out] // Wishbone termination w/ error (optional)

wb_rty_o – [out] // Wishbone termination w/ retry (optional)

This define is for the testbench and as a template, this MUST be changed when used for a custom design. The define should then be at /hw/piconut/config.mk .

#define CFG_WB_SLAVE_TEMPLATE_ADDRESS 0xF0000000

Wishbone Read

A simple wishbone read cycle is displayed in the image below.

Fig. 11 Diagramm of a simple read access via the Wishbone bus protocol.

Wishbone Write

A simple wishbone write cycle is displayed in the image below.

Fig. 12 Diagramm of a simple write access via the Wishbone bus protocol.

Wishbone Byte Select

The bus supports the byte select signal which is four bits wide. You can precisely select every eight bit word in the register for writing and reading.

Examples in a binary and hexadecimal representation:

0b1111 = 0xF The all four bytes will be used.

0b1100 = 0xC The two upper bytes will be used.

0b0010 = 0x2 The second lowest byte will be used.

0b0001 = 0x1 The lowest byte will be used.